ZL30102

Overview

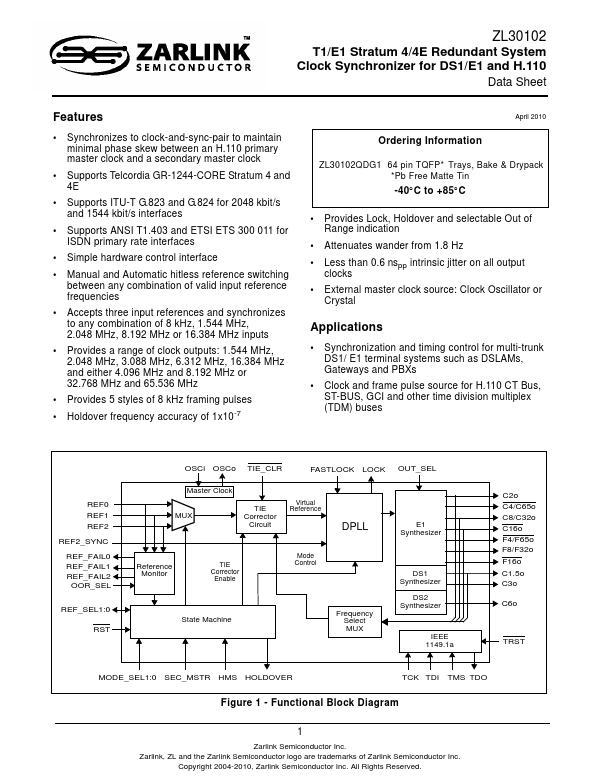

- Synchronizes to clock-and-sync-pair to maintain minimal phase skew between an H.110 primary master clock and a secondary master clock

- Supports Telcordia GR-1244-CORE Stratum 4 and 4E

- Supports ITU-T G.823 and G.824 for 2048 kbit/s and 1544 kbit/s interfaces

- Supports ANSI T1.403 and ETSI ETS 300 011 for ISDN primary rate interfaces

- Simple hardware control interface

- Manual and Automatic hitless reference switching between any combination of valid input reference frequencies

- Accepts three input references and synchronizes to any combination of 8 kHz, 1.544 MHz, 2.048 MHz, 8.192 MHz or 16.384 MHz inputs

- Provides a range of clock outputs: 1.544 MHz, 2.048 MHz, 3.088 MHz, 6.312 MHz, 16.384 MHz and either 4.096 MHz and 8.192 MHz or 32.768 MHz and 65.536 MHz

- Provides 5 styles of 8 kHz framing pulses

- Holdover frequency accuracy of 1x10-7 April 2010